# ON THE REALIZATION OF FLOATING INDUCTORS

#### AHMED M SOLIMAN

Electronics and Communications Engineering Department, Cairo University, Egypt

E-mail: asoliman@ieee.org

**ABSTRACT:** Floating inductor circuits using minimum number of passive elements namely two resistors and one capacitor is reviewed in this paper. All the circuits considered in this paper are floating. Previously reported non-floating circuits are modified to be floating and new floating circuits are introduced as well. The active elements used in this paper are floating conveyor building blocks as well as pairs of non-floating conveyor blocks acting as a floating pair. Simulation results of second order lowpass filters realized using different types of floating inductors are included. [Nature and Science 2010;8(5):167-180]. (ISSN: 1545-0740).

Keywords: Floating inductors, current conveyors, gyrator, DVCC, FDVCC.

#### 1. INTRODUCTION

The classification of active RC circuits simulating floating inductors was given in [1]. The floating inductor circuits reported in [1] employ the operational amplifier (Op Amp) or the nullor element [2] known also as the operational floating amplifier (OFA) [3] as the active building block. Detailed derivation of the admittance matrix equation of different types of gyrators was given in [1]. A single Op Amp gyrator realization was introduced in [4]. Gyrator realization using two second generation current conveyors (CCII) with opposite Z polarities was introduced in [5]. The use of single CCII- in realizing non-ideal inductor was first introduced in [6] followed by a single CCII+gyrator circuit [7].

Simulated ideal floating inductors using CCII and transconductance amplifiers (TA) was classified and reviewed in [8] and new CCII floating gyrator circuits were given.

Most recently generation method of floating ideal inductors based on using nodal admittance matrix (NAM) expansion [9-10] was introduced in [11]. This paper concentrates on the realization of floating inductors using floating gyrator circuits and a single capacitor. The total number of resistors in each of the gyrator circuits considered is limited to two resistors.

# 2. GENERALIZED INDUCTOR CONFIGURATIONS

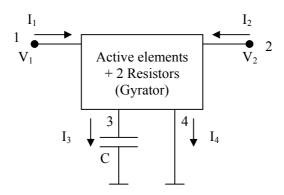

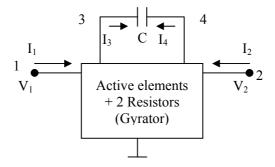

Figures 1(a) and 1(b) represent the two generalized configurations defined as types A and B realizing floating inductors in accordance with the classification given in [1]. The circuit shown in Figure 1(a) includes two general cases depending on the summation of the four currents.

If the summation  $I_1+I_2+I_3+I_4$  is not zero the circuit is not floating. On the other hand a necessary condition that the circuit is floating is given by [1]:

$$I_1 + I_2 + I_3 + I_4 = 0 (1)$$

Most of the floating inductor circuits that belong to the generalized configuration shown in Figure 1(a) in which the capacitor is grounded are not floating. Table 3 in [8] includes nine gyrator circuits that belong to this case.

Six generalized configurations that belong to type A, and realize floating inductors satisfying the condition of equation (1) are given in this paper. Six generalized configurations that belong to type B are also given in this paper.

Figure 1(a) Generalized Type A configuration

Figure 1(b) Generalized Type B configuration

The first active building block that is used in the paper is the generalized conveyor (GC) defined by the following matrix equation:

$$\begin{bmatrix} \mathbf{I}_{\mathbf{Y}} \\ \mathbf{V}_{\mathbf{X}} \\ \mathbf{I}_{\mathbf{Z}} \end{bmatrix} = \begin{bmatrix} \mathbf{0} & \mathbf{0} & \mathbf{0} \\ \mathbf{a} & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{K} & \mathbf{0} \end{bmatrix} \begin{bmatrix} \mathbf{V}_{\mathbf{Y}} \\ \mathbf{I}_{\mathbf{X}} \\ \mathbf{V}_{\mathbf{Z}} \end{bmatrix}$$

(2)

The parameter a determines the type of the GC, a CCII is realized if a = 1 and ICCII is obtained if a = -1. The parameter K determines the Z polarity of the GC, for Z+ the parameter K = 1 and for Z- the parameter K = -1.

The GC includes four different types; the CCII– and the ICCII– are floating whereas the CCII+ and ICCII+ are not floating. The CCII+ and ICCII+ although non-floating can also be used in realizing floating circuits provided they are used in pairs as will be demonstrated in the next section.

Table 1 includes a summary of the floating conveyor building blocks that will be used in this paper.

# 3. TYPE A INDUCTOR CIRCUITS

In this section six floating circuits realizing floating inductors satisfying the condition of equation (1) and using two resistors and one capacitor are given.

Table 1 Floating building blocks used in the paper

| Table 1 Floating building blocks used in the paper |                                                                                                                                                                                                                   |                                                                                                                           |  |  |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Conveyor                                           | Definition                                                                                                                                                                                                        | Floating Building Block Symbol                                                                                            |  |  |  |  |  |

| CCII- [5]                                          | $\begin{bmatrix} I_{Y} \\ V_{X} \\ I_{Z} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & -1 & 0 \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{X} \\ V_{Z} \end{bmatrix}$                                | $\begin{array}{c c} & & & & & I_{Z-} \\ & & & & & & I_{Z-} \\ \hline & & & & & & \\ \hline & & & & & & \\ \hline & & & &$ |  |  |  |  |  |

| ICCII-[12]                                         | $\begin{bmatrix} I_{Y} \\ V_{X} \\ I_{Z} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ -1 & 0 & 0 \\ 0 & -1 & 0 \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{X} \\ V_{Z} \end{bmatrix}$                               | $\begin{array}{c c} & & & & I_{Z-} \\ \hline & & & & & \\ \hline & & & & \\ \hline & & & & \\ \hline & & & &$             |  |  |  |  |  |

| DVCC- [13]                                         | $\begin{bmatrix} Vx \\ IY1 \\ IY2 \\ I Z- \end{bmatrix} = \begin{bmatrix} 0 & 1 & -1 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ -1 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} Ix \\ VY1 \\ VY2 \\ VZ- \end{bmatrix}$ | $\begin{array}{c c} & & & & I_{Z} \\ & & & & & I_{Z} \\ & & & & & & \\ & & & & & & \\ & & & & $                           |  |  |  |  |  |

| FDVCC<br>[New]                                     | $\begin{bmatrix} V_X \\ I_{Y1} \\ I_{Y2} \\ I_{Z+} \\ I_{Z1-} \\ I_{Z2-} \end{bmatrix} = \begin{bmatrix} 0 & 1 & -1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 &$                                              | $Y_{1} \qquad Z_{+}$ $Y_{2} \qquad FDVCC$ $Z_{1-}$ $X \qquad Z_{2-}$ $I_{X}$ $I_{G}=0$                                    |  |  |  |  |  |

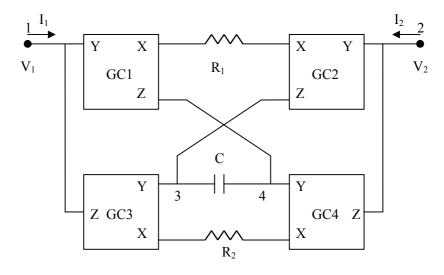

## 3.1. Four Generalized Conveyor Circuit

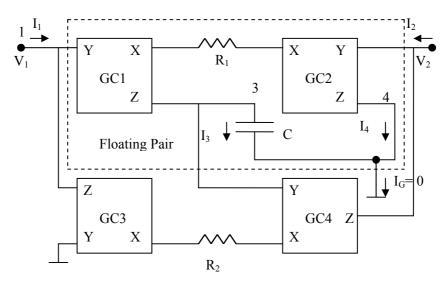

The configuration shown in Figure 2 using four nullors was first reported in [1]. The generalized configuration using four CCII+ realized from operational amplifiers (Op Amps) together with current mirrors was first reported in [14] and republished in [15] with a comment given in [16]. The generalized configuration using four CCII– (equivalent to four nullors) was reported in [8]. The same generalized configuration using four ICCII– was reported in [17].

The circuit shown in Figure 2 employs four GC and a necessary condition for  $V_1$  and  $V_2$  to appear in a subtraction form is that  $a_1 = a_2$ . A necessary condition for the circuit to be floating is that  $K_1 = K_2$ . These two conditions imply that GC1 and GC2 must be matched.

Figure 2. A floating inductor using four generalized conveyor

A necessary condition for the current  $I_1$  to equal to  $-I_2$  is that  $K_3 = K_4$ .

Although  $a_3$  can be either 1 or -1 and has no effect on circuit operation it is taken equal to  $a_4$  for a symmetrical circuit. Therefore GC3 and GC4 are taken to be matched.

By direct analysis it can be shown that:

$$I1 = -I2 = \frac{V1 - V2}{sCR1R2} \left[ a_1 K_1 a_3 K_3 \right]$$

(3)

A necessary condition for a floating inductor realization is that  $a_1K_1a_3K_3$  must be  $\pm 1$ . Eight possible conveyor realizations are given in Table 2 that satisfies this coefficient condition. It is seen that this approach of analysis resulted in five new conveyor circuits.

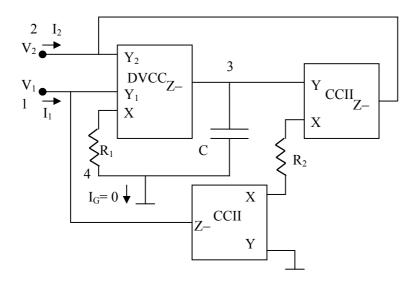

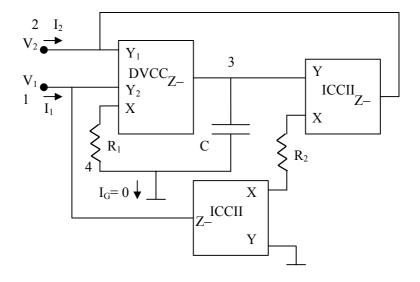

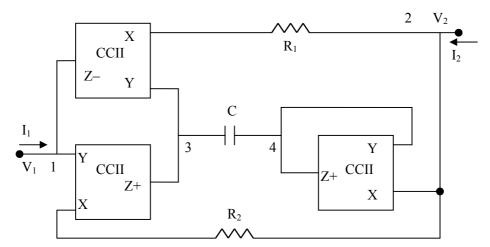

## 3.2 DVCC- and Two CCII- Or Two ICCII- Circuits

The circuit shown in Figure 3(a) is a modified version of the newly reported DVCC and two CCII+ circuit shown in Figure 14 of [11] by replacing the two CCII+ by two CCII-. The circuit is floating since  $I_G$  is zero and it realizes a floating inductor given by  $CR_1R_2$ .

Figure 3(b) represents a second equivalent floating circuit which uses two ICCII– instead of the two CCII– in Figure 3(a).

# 3.3 Two Floating DVCC Circuits

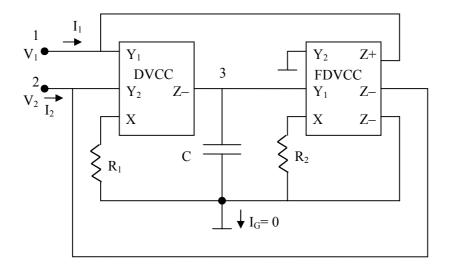

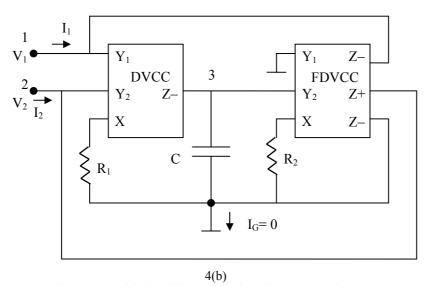

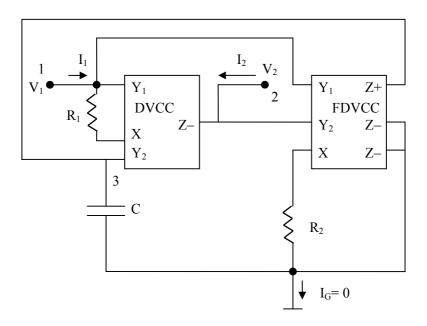

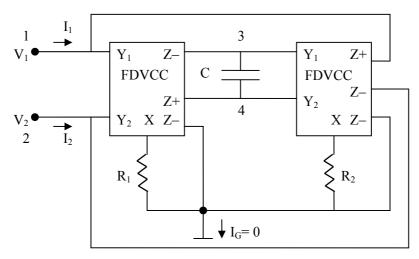

The two floating circuits shown in Figure 4 are new and they are obtained from the newly reported circuit shown in Figure 16 of [11]. The circuits employ the DVCC– and the newly defined floating DVCC (FDVCC) given in Table 1.

The third circuit is shown in Figure 5 is a modified version of the floating inductor circuit proposed in [18] by using the FDVCC instead of the DVCC+ in [18].

The three circuits shown in Figures 4 and 5 are floating since  $I_G$  is zero and each realizes a floating inductor given by  $CR_1R_2$ .

Figure 3(a) A floating inductor using a DVCC and two CCII-[11]

Figure 3(b) Alternative floating inductor using a DVCC and two CCII-

# 4. TYPE B INDUCTOR CIRCUITS

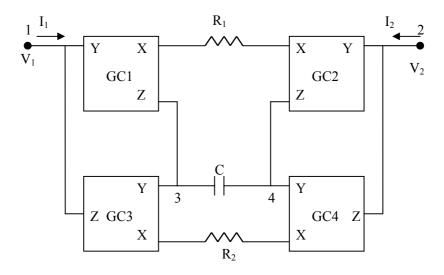

The circuit shown in Figure 6(a) is a modified version of the circuit of Figure 2. It was introduced in [1] using four nullors and in [19] using four CCII– or four CCII+, it was also reported in [8] using four CCII–. The GC1 and GC2 must be identical types; also GC3 and GC4 must be identical types. The types of conveyors given in Table 2 apply to this floating circuit also.

An alternative generalized configuration realizing a floating inductor is shown in Figure 6(b). The GC1 and GC2 must be identical types; also GC3 and GC4 must be identical types. By direct analysis it can be shown that:

$$I1 = -I2 = -\frac{V1 - V2}{sCR1R2} \left[ a_1 K_1 a_3 K_3 \right]$$

(4)

A necessary condition for a floating inductor realization is that  $a_1K_1a_3K_3$  must be -1. Eight possible conveyors realizations are given in Table 3 that satisfies this coefficient condition. It is seen that seven new circuits are generated based on this circuit topology.

Figure 4(a)

Figure 4 Two floating inductor circuits using DVCC and FDVCC [11]

Figure 5 A modified floating inductor using DVCC and FDVCC [18]

Figure 6(a) A floating inductor using four generalized conveyors [19]

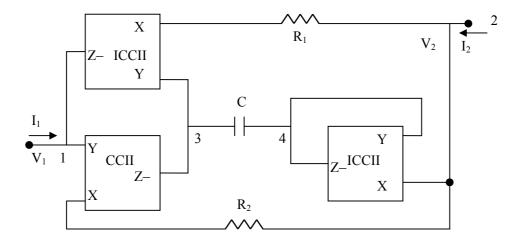

Figure 7(a) represents a floating inductor circuit using two CCII+ and one CCII- [20]. This is among the four floating gyrator circuits reported in [8]. A new modified floating inductor circuit using two ICCII- and one CCII-is shown in Figure 7(b).

Figure 8(a) represents a modified floating inductor circuit to the two DVCC circuit reported in [21] using two FDVCC in order to have a floating circuit with  $I_G$  equal to zero. An alternative new equivalent circuit is shown in Figure 8(b). Both circuits realize an inductor of magnitude  $CR_1R_2$ .

Figure 6(b) Alternative floating inductor using four generalized conveyors

Figure 7(a) A floating inductor using two CCII+ and one CCII– [20]  $\,$

Figure 7(b) A new floating inductor using two ICCII- and one CCII-

Figure 8(a) A modified floating inductor using two DVCC [21].

Figure 8(b) Alternative modified floating inductor using two DVCC.

Figure 9 CMOS circuit of the floating DVCC [21]

## 5. SIMULATION RESULTS

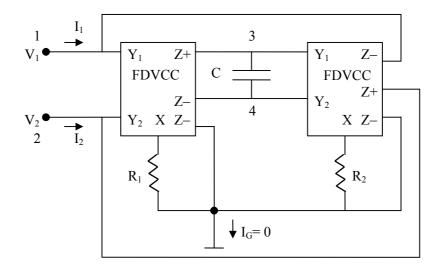

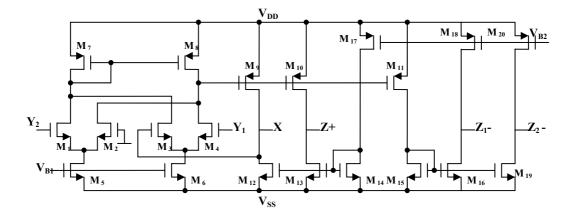

The CMOS circuit realizing the FDVCC is obtained directly from the well known DVCC [21] by adding the two MOS transistors  $M_{19}$  and  $M_{20}$  as shown in Figure 9.

The transistor aspect ratios are given in Table 4 based on the 0.5 $\mu$ m CMOS model from MOSIS. The supply voltages used are  $\pm$  1.5 V and  $V_{B1}$ = -0.52 V and  $V_{B2}$  = 0.33 V.

This circuit will be used in the following simulations to realize different types of conveyors.

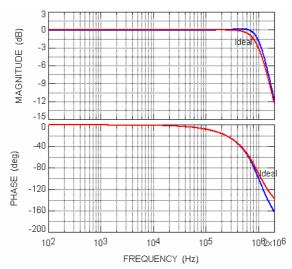

As an application of some of the floating circuits reported, a floating inductor of magnitude 0.253 m. H is realized taking the capacitor C =100pFand  $R_1 = R_2 = 1.59 \text{ k}\Omega$ . The floating inductor is used to realize a maximally flat (Q=0.707) second order low-pass filter with cutoff frequency of 1MHz using a series resistor of  $R_S = 2.25 \text{ k}\Omega$  and  $C_S$  of 100pF.

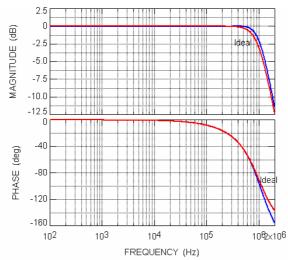

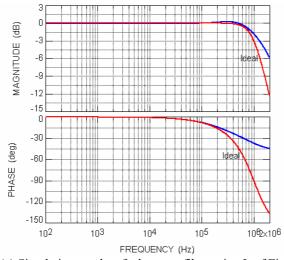

Figure 10(a) represents the simulated magnitude and phase responses together with the ideal responses using the inductor circuit of Figure 2 with four ICCII+.

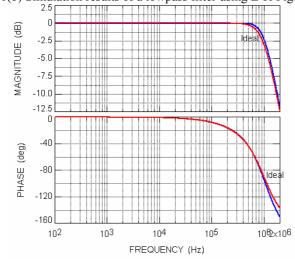

Figure 10(b) represents the simulated magnitude and phase responses together with the ideal responses using the inductor circuit of Figure 3(a).

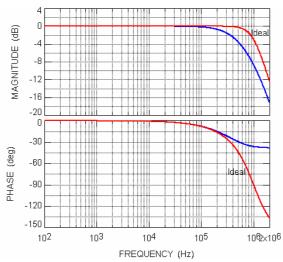

Figure 10(c) represents the simulated magnitude and phase responses together with the ideal responses using the inductor circuit of Figure 5.

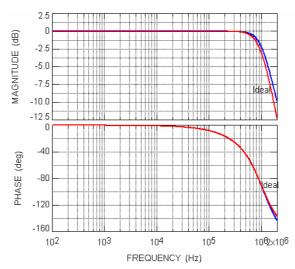

Figure 11(a) represents the simulated magnitude and phase responses together with the ideal responses using the inductor circuit of Figure 6(b) with four ICCII+.

Figure 11(b) represents the simulated magnitude and phase responses together with the ideal responses using the inductor circuit of Figure 7(b).

Figure 11(c) represents the simulated magnitude and phase responses together with the ideal responses using the inductor circuit of Figure 8(b).

| Table 2 Eight alternative | conveyor circuits | based on Figure 2 |

|---------------------------|-------------------|-------------------|

| 8                         |                   |                   |

| Circuit | $a_1, a_2$ | $K_1, K_2$ | $a_3, a_4$ | K <sub>3</sub> , K <sub>4</sub> | $GC_1,GC_2$ | $GC_3$ , $GC_4$ | Ref   |

|---------|------------|------------|------------|---------------------------------|-------------|-----------------|-------|

| 1       | +          | +          | +          | +                               | CCII+       | CCII+           | 14–16 |

| 2       | +          | -          | +          | _                               | CCII-       | CCII-           | 1, 8  |

| 3       | _          | _          | +          | +                               | ICCII–      | CCII+           | New   |

| 4       | +          | +          | _          | _                               | CCII+       | ICCII–          | New   |

| 5       | _          | +          | _          | +                               | ICCII+      | ICCII+          | New   |

| 6       | _          | +          | +          | _                               | ICCII+      | CCII–           | New   |

| 7       | +          |            | _          | +                               | CCII-       | ICCII+          | New   |

| 8       | _          |            | _          | _                               | ICCII-      | ICCII-          | 17    |

Table 3 Eight alternative conveyor circuits based on Figure 6(b)

| Circuit | $a_1, a_2$ | $K_1, K_2$ | $a_3, a_4$ | $K_3, K_4$ | $GC_1,GC_2$ | $GC_3$ , $GC_4$ | Ref |

|---------|------------|------------|------------|------------|-------------|-----------------|-----|

| 1       | +          | _          | +          | +          | CCII–       | CCII+           | 8   |

| 2       | +          | +          | +          | _          | CCII+       | CCII–           | New |

| 3       | _          | +          | +          | +          | ICCII+      | CCII+           | New |

| 4       | +          | +          | _          | +          | CCII+       | ICCII+          | New |

| 5       | +          | _          | _          | _          | CCII–       | ICCII–          | New |

| 6       | _          | +          | _          | _          | ICCII+      | ICCII–          | New |

| 7       | _          | _          | +          | _          | ICCII–      | CCII–           | New |

| 8       | _          | _          | _          | +          | ICCII-      | ICCII+          | New |

### 6. CONCLUSIONS

Realization of ideal inductor circuits using different types of conveyor building blocks is reviewed. Two types of inductor circuits are defined as was originally classified in [1]. The FDVCC is defined and is used in several circuits in this paper. Spice simulation results are given. Although this paper is partially a review paper it includes several new floating circuits

Figure 10(a) Simulation results of a lowpass filter using L of Figure 2

Fig 10(b) Simulation results of a lowpass filter using L of Figure 3(a)

Fig 10(c) Simulation results of a lowpass filter using L of Figure 5

Fig 11(a) Simulation results of a lowpass filter using L of Figure 6(b)

Fig 11(b) Simulation results of a lowpass filter using L of Figure 7(b)

Fig 11(c) Simulation results of a lowpass filter using L of Figure 8(b)

Table 4 Transistor aspect ratios of the FDVCC of Figure 9

| MOS Transistors                                                                                          | W(μm)/L(μm) |

|----------------------------------------------------------------------------------------------------------|-------------|

| $M_1, M_2, M_3, M_4$                                                                                     | 8/1         |

| $M_5$ , $M_6$                                                                                            | 8/1         |

| $M_{12}, M_{13}, M_{14}, M_{15}, M_{16}, M_{17}$                                                         | 20/2.5      |

| $M_7, M_8$                                                                                               | 10/1        |

| M <sub>9</sub> , M <sub>10</sub> , M <sub>11</sub> , M <sub>18</sub> , M <sub>19</sub> , M <sub>20</sub> | 40/2        |

## 7. REFRENCES:

- [1] M. Silva and W. Saraga ,On the classification of active *RC* circuits simulation floating inductors, *Proc. Third Int. Symposium On Network Theory*, 1975, pp. 489-496.

- [2] H. J. Carlin, Singular network elements, IEEE Trans. Circuit Theory, Vol. 11, 1964, pp 67-72.

- [3] J.H. Huijsing, Design and applications of the operational floating amplifier (OFA): The most universal operational amplifier. *Analog Integrated Circuits and Signal Processing*, ,Vol.4, 1993, pp 115-129.

- [4] H. J. Orchard and A. Willson. New active gyrator circuit, *Electronics letters*, Vol.10, 1974, pp 261-262.

- [5] A.S, Sedra and K.C. Smith, A second generation current conveyor and its applications, *IEEE Trans. Circuit Theory*, Vol. 132, 1970 pp 132-134.

- [6] A. M. Soliman, Ford-Girling equivalent circuit using CCII, *Electronics Letters*, Vol.14, 1978, pp 721-722.

- [7] A.M. Soliman, New Active Gyrator Circuit Using a Single Current Conveyor, *Proceedings IEEE*, Vol. 66, 1978, pp 1580-1581.

- [8] M.C, Layos and I. Haritantis, On the derivation of current-mode floating inductors. *International Journal of Circuit Theory and Applications*, Vol. 25, 1997, pp 29–36.

- [9] D. G. Haigh, F.Q. Tan and C. Papavassiliou, Systematic synthesis of active-RC circuit building-blocks. *Analog Integrated Circuits and Signal Processing*, Vol. 43(3), 2005, pp 297–315.

- [10] D. G. Haigh, T. J. W.Clarke and P.M. Radmore, Symbolic framework for linear active circuits based on port equivalence using limit variables. *IEEE Trans. Circuits Systems I*, Vol. 53(9), 2006, pp 2011–2024.

- [11] R. A Saad and A.M. Soliman, On the systematic synthesis of CCII based floating simulators. *International Journal of Circuit Theory and Applications*, 2009; DOI: 10.1002/cta.604.

- [12] I.A. Awad and A.M. Soliman, Inverting second-generation current conveyors: the missing building blocks, CMOS realizations and applications. *Int. Journal of Electronics*, Vol. 86, 1999, pp. 413-432.

- [13] A.M. Soliman, On the DVCC and the BOCCII as adjoint elements, *Journal of Circuits, Systems and Computers*, Vol. 18, 2009, pp 1017-1032.

- [14] C. Toumazou and J. Lidgey, Floating impedance converters using current conveyors, Electronics Letters, Vol. 21, 1985, pp 640-642.

- [15] W. Kiranon and P. Pawarangkoon, Floating inductance simulation based on current conveyors. *Electronics Letters*, Vol. 33, 1997, pp 1748–1749.

- [16] M.T.Aboulmaatti, Comment on floating inductance simulation based on current conveyors, *Electronics Letters*, Vol. 34, 1998, pp 1037-1038.

- [17] E. Sobhy and A.M. Soliman, Novel CMOS realizations of the inverting second-generation current conveyor and applications, *Analog Integrated Circuits and Signal Processing*, Vol. 5, 2007, pp 57-64.

- [18] J.W. Horng, Lossless inductance simulation and voltage mode universal bi-quadratic filter with one-input-and five outputs using DVCC. Analog Integrated Circuits and Signal Processing , Online 2009

- [19] C. Toumazou , J. Lidgey J, and A. Payne, Emerging Techniques for High Frequency BJT Amplifier Design: A Current Mode Perspective, The *First International conference on*

Electronics, Circuits and Systems, Cairo, Egypt 1994, pp.57.

[20] R. Senani, New tunable synthetic floating inductors, *Electronics Letters*, Vol. 16:, 1980, pp 382-383

[21] H.O.Elwan and A.M. Soliman, A novel CMOS differential voltage current conveyor and its applications, *IEE Proceedings, Circuits, Devices and Systems*, Vol. 144, 1997, pp 195–200.

## **BIOGRAPHY:**

**Ahmed M. Soliman** was born in Cairo Egypt, on November 22, 1943. He received the B.Sc. degree with honors from Cairo University, Cairo, Egypt, in 1964, the M.S. and Ph.D. degrees from the University of Pittsburgh, Pittsburgh, PA., U.S.A., in 1967 and 1970, respectively, all in Electrical Engineering. He is currently Professor Electronics and Communications Engineering Department, Cairo University, Egypt.

From September 1997-September 2003, Dr Soliman served as Professor and Chairman Electronics and Communications Engineering Department, Cairo University, Egypt.

From 1985-1987, Dr. Soliman served as Professor and Chairman of the Electrical Engineering Department, United Arab Emirates University, and from 1987-1991 he was the Associate Dean of Engineering at the same University.

He has held visiting academic appointments at San Francisco State University, Florida Atlantic University and the American University in Cairo.

He was a visiting scholar at Bochum University, Germany (Summer 1985) and with the Technical University of Wien, Austria (Summer 1987).

In 1977, Dr. Soliman was decorated with the First Class Science Medal, from the President of Egypt, for his services to the field of Engineering and Engineering Education.

Dr Soliman is a Member of the Editorial Board of the IET Proceedings Circuits, Devices and Systems.

Dr Soliman is a Member of the Editorial Board of Electrical and Computer Engineering.

Dr Soliman is a Member of the Editorial Board of Analog Integrated Circuits and Signal Processing.

Dr Soliman is also a Member of the Editorial Board of Scientific Research and Essays.

Dr Soliman served as Associate Editor of the IEEE Transactions on Circuits and Systems I (Analog Circuits and Filters) from December 2001 to December 2003 and is Associate Editor of the Journal of Circuits, Systems and Signal Processing from January 2004-Now.

3/9/2010